In today’s fast-paced world, communication and data exchange are crucial elements for the success of any system or device. The design of modern integrated circuits (ICs) faces numerous challenges when it comes to efficient interconnectivity. That’s where Network on a Chip (NoC) comes into play.

NoC is an innovative architecture that provides a scalable and efficient communication fabric for ICs. It offers a versatile and flexible topology that enables high integration of various system components, such as processors, memories, and peripherals.

One of the key advantages of NoC is its scalability. Traditional IC designs face limitations in terms of the number of interconnects they can accommodate, which restricts their ability to handle complex tasks and large amounts of data. NoC, on the other hand, allows for the integration of a large number of cores and components, resulting in improved system performance and efficiency.

Another important aspect of NoC is its energy efficiency. By utilizing advanced routing and protocol mechanisms, NoC minimizes the amount of energy required for data transmission, making it a viable solution for power-sensitive applications. This efficiency translates into longer battery life for portable devices and reduced energy consumption for larger systems.

Contents

- 1 What is a Network on a Chip?

- 2 Benefits of Network on a Chip

- 3 Applications of Network on a Chip

- 4 Embedded Systems

- 5 Internet of Things

- 6 Design and Implementation of Network on a Chip

- 7 Architecture

- 8 Testing and Verification

- 9 Future Trends and Challenges

- 10 Integration with Artificial Intelligence

- 11 Security and Privacy

- 12 FAQ about topic “Network on a Chip: Expanding the Possibilities of Integrated Circuits”

- 13 What is Network on a Chip (NoC)?

- 14 What are the advantages of using Network on a Chip (NoC) in integrated circuits?

- 15 How does Network on a Chip (NoC) address the challenges of traditional bus-based interconnects?

- 16 What are the current research areas in Network on a Chip (NoC) technology?

- 17 What are the applications of Network on a Chip (NoC) technology?

What is a Network on a Chip?

A Network on a Chip (NoC) is an integration of multiple communication interconnects on a single chip, designed to improve the performance, efficiency, and scalability of a system. It is a fabric-like interconnect that enables efficient routing and communication between different components within a chip.

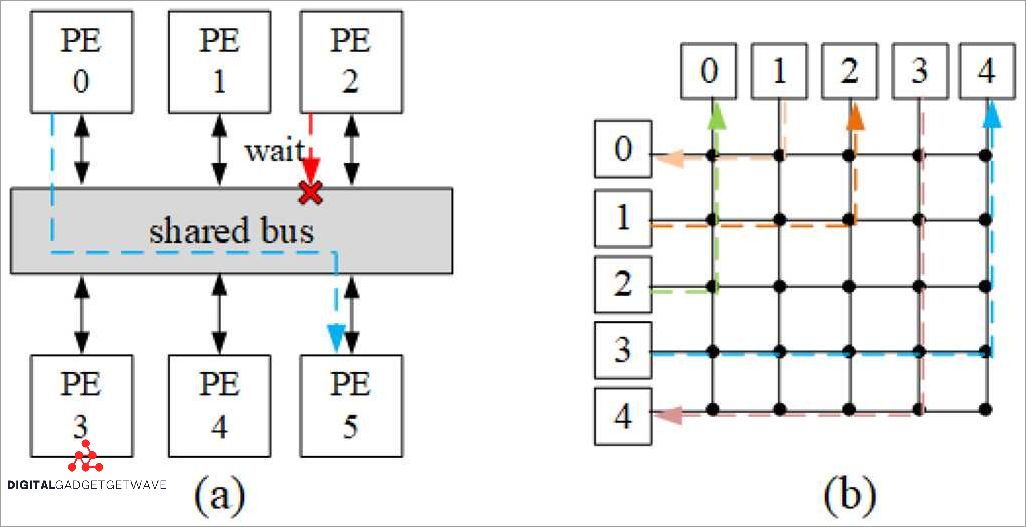

The NoC architecture is specifically designed to address the limitations of traditional bus-based communication systems by providing a more flexible and efficient interconnect. It replaces the centralized bus with a distributed network, allowing for parallel communication and reducing the bottlenecks that can occur in bus-based systems.

One of the key advantages of using a NoC is its scalability. With the increasing complexity of integrated circuits and the growing demand for more functionality, a NoC allows for seamless integration of multiple cores, IP blocks, and other components, enabling the design of more powerful and feature-rich systems.

In addition to scalability, a NoC also offers improved energy efficiency. By using packet-based communication instead of the traditional wire-based communication, a NoC can reduce the energy consumption of a chip. It also enables dynamic power management techniques, such as power gating and voltage scaling, to further optimize the energy efficiency of the system.

The design of a NoC involves creating a topology that connects different components within the chip. This topology can vary depending on the specific requirements of the system, such as latency, bandwidth, and reliability. Some popular topologies include mesh, tree, and ring, each offering different trade-offs in terms of performance and complexity.

In conclusion, a Network on a Chip is a powerful and efficient communication infrastructure that enhances the integration, performance, and energy efficiency of integrated circuits. By providing a flexible and scalable interconnect, it enables the design of complex systems while optimizing the energy consumption of the chip.

Definition and Functionality

A Network on a Chip (NoC) is a design concept and architecture for integrating multiple components or subsystems on a single chip in a system-on-chip (SoC) design. It provides a scalable and efficient interconnect fabric that enables communication and data exchange between different components within the chip.

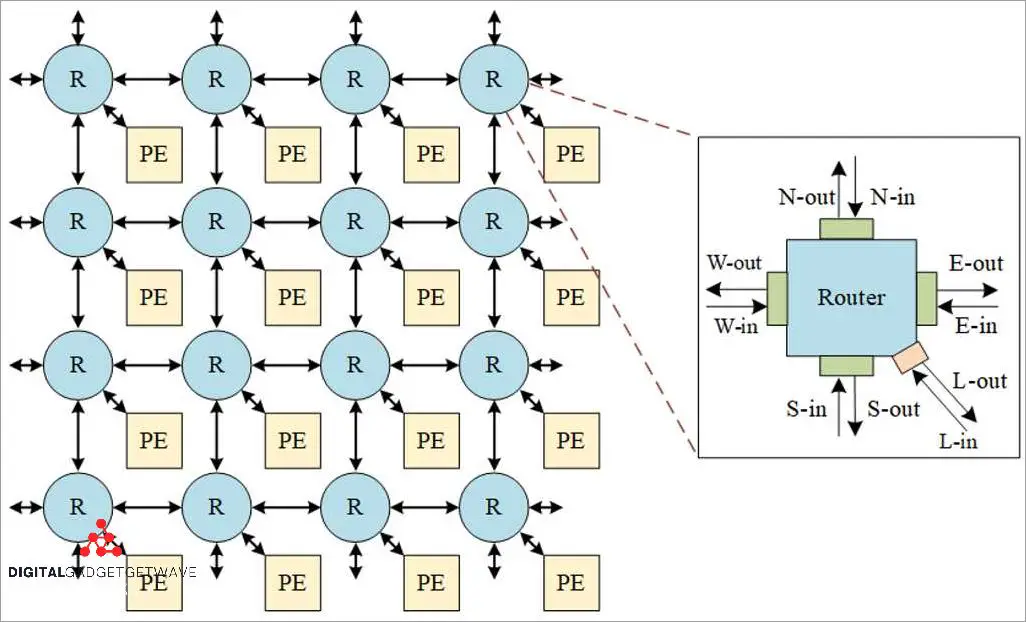

The NoC topology consists of a network of processing elements, memories, and other components interconnected by a set of routers and links. The routers are responsible for routing packets of data from one component to another, while the links provide the physical channels for data transfer.

The main goal of a NoC is to improve the performance and energy efficiency of integrated circuits by providing a high-bandwidth and low-latency communication infrastructure. It offers a flexible and reconfigurable interconnect layout, allowing for easy integration of new components or subsystems into the chip design.

The design of a NoC incorporates various routing algorithms and protocols that determine how data is transmitted and routed between different components. These routing algorithms optimize the use of available resources, minimize congestion, and ensure efficient data transfer across the network.

The scalability of a NoC is an important aspect, as it allows for easy integration of an increasing number of components into the chip design without sacrificing performance or energy efficiency. This is achieved by designing the network with a modular and hierarchical structure that can efficiently handle a growing number of interconnects.

In conclusion, a Network on a Chip provides a highly efficient and scalable communication infrastructure for integrating components and subsystems on a single chip. Its design and architecture ensure high performance, energy efficiency, and flexibility for the integration of new components into the chip. This makes NoCs a promising solution for future integrated circuits.

Benefits of Network on a Chip

The integration of a Network on a Chip (NoC) within an integrated circuit brings numerous benefits to the design and performance of electronic systems. Here are some of the key advantages:

- Scalability: NoC enables the design of highly scalable systems by using a router-based communication architecture. This allows for easy expansion and addition of components without major redesign.

- Efficiency: The use of a protocol-based communication system and routing algorithms ensures efficient data transfer, reducing latency and improving system performance.

- Energy Efficiency: NoC design allows for power management strategies such as dynamic voltage and frequency scaling, which optimize energy consumption by adjusting the voltage and frequency of individual components.

- Interconnects: NoC provides robust and flexible interconnects that can handle the increasing complexities of modern integrated circuits. It ensures reliable and high-bandwidth communication between various components.

- Topology: NoC offers the flexibility to choose different network topologies based on the specific application requirements. It allows for the design of customized architectures that are optimized for specific communication patterns and data flows.

- Integration: NoC simplifies the integration of multiple cores, memories, and peripherals into a single chip. It facilitates the communication between different IP blocks, enabling efficient sharing of resources and data.

- Design Productivity: NoC provides a standardized interface between different components, enabling modular design and faster development cycles. It promotes reuse of IP cores and simplifies system integration.

In conclusion, Network on a Chip offers a wide range of benefits including scalability, efficiency, energy optimization, robust interconnects, flexible topology options, easy integration, and improved design productivity. These advantages make NoC a promising technology for expanding the possibilities of integrated circuits in various applications.

Increased Performance and Scalability

As the demand for faster and more efficient communication between system components continues to grow, the need for a high-performance and scalable network fabric becomes increasingly important. The development of Network-on-Chip (NoC) technology addresses this challenge by offering a sophisticated interconnect solution that greatly enhances the performance and efficiency of integrated circuits.

One of the key factors contributing to the increased performance of NoC is its highly scalable architecture. NoC provides a flexible and modular interconnect design that allows for easy integration of multiple cores and IP blocks on a chip. This scalability enables designers to build complex systems with hundreds or even thousands of interconnected components, providing a significant boost in computing power and overall system performance.

Another advantage of NoC is its efficient routing protocol. NoC uses advanced routing algorithms to efficiently route data packets across the network fabric, minimizing congestion and reducing latency. This efficient routing scheme ensures that data is delivered quickly and reliably, further enhancing the performance of the system.

In addition to improved performance, NoC also offers enhanced energy efficiency. Traditional bus-based interconnects suffer from high energy consumption due to the large number of wires required for communication. NoC, on the other hand, uses a packet-based communication scheme that significantly reduces the number of wires needed, resulting in lower energy consumption and improved power efficiency.

The topology of a NoC also plays a crucial role in its performance and scalability. NoC can be designed with various topologies, such as mesh, torus, or tree structures, depending on the specific requirements of the system. Each topology offers different benefits in terms of bandwidth, latency, and fault tolerance, allowing designers to choose the most suitable topology for their application.

In conclusion, Network-on-Chip technology provides a powerful and flexible interconnect solution that significantly enhances the performance and scalability of integrated circuits. With its scalable architecture, efficient routing protocol, energy efficiency, and customizable topology, NoC offers a game-changing approach to system design and communication.

Improved Power Efficiency

The design of Network on a Chip (NoC) architectures brings significant improvements in power efficiency compared to traditional interconnect designs. A key aspect of this improvement lies in the topology of the network, which is specifically designed to minimize power consumption.

NoC uses a structured network that connects various components of a chip through a mesh or a tree-like interconnect fabric. This optimized and efficient interconnect design reduces power dissipation by minimizing the length of the interconnects and reducing the number of wire crossings. This topology ensures that communication between different components is efficient and consumes less energy.

In NoC, routing protocols play a vital role in achieving improved power efficiency. These protocols guide the flow of data packets through the network, ensuring that they take the shortest and most energy-efficient paths. By intelligently routing the packets, the NoC architecture minimizes energy consumption, resulting in improved power efficiency.

Another factor that contributes to improved power efficiency in NoC is its scalable nature. NoC architectures can be easily scaled up or down depending on the system requirements. This scalability ensures that energy consumption remains low even when the network size increases. The ability to efficiently manage larger networks without sacrificing power efficiency is a significant advantage of NoC architectures.

Overall, the utilization of NoC architecture in integrated circuits enhances power efficiency by optimizing the interconnect design, implementing efficient routing protocols, and providing scalability. This improved power efficiency allows for better performance and reduced energy consumption in various applications, making NoC a promising technology for future chip designs.

Applications of Network on a Chip

The integration of network on a chip (NoC) technology into integrated circuits has opened up a wide range of possibilities and applications. NoC provides a scalable and efficient solution for on-chip communication, enabling high-performance and energy-efficient designs.

One of the key applications of NoC is in the design of system-on-chip (SoC) architectures. By using NoC, multiple IP cores can be interconnected efficiently, allowing for better communication and coordination between different components of the SoC. NoC also enables the integration of various protocols and interconnects, making it ideal for complex system designs.

NoC is particularly beneficial for applications that require high bandwidth and low latency, such as multimedia and real-time systems. The use of NoC allows for efficient routing and communication between different processing units, resulting in improved system performance. The scalable nature of NoC also ensures that the system can easily handle increasing data traffic and maintain high communication speeds.

Another application of NoC is in the design of energy-efficient integrated circuits. NoC provides a power-efficient solution for on-chip communication by optimizing the routing and data transfer processes. This reduces the overall energy consumption of the chip and improves its performance per watt.

NoC can also be used in the development of advanced network architectures, such as mesh and torus topologies. These topologies provide efficient communication paths between different cores, ensuring that data can be transmitted quickly and efficiently. This is especially important in parallel processing applications, where high-speed communication between cores is crucial for achieving optimal performance.

In conclusion, the applications of network on a chip are diverse and far-reaching. From system-on-chip designs to energy-efficient integrated circuits and advanced network architectures, NoC technology offers a flexible and efficient solution for on-chip communication. Its scalability, efficiency, and performance-enhancing features make it a valuable tool for developers and designers in the field of integrated circuits.

Embedded Systems

An embedded system is a computer system with a dedicated function within a larger mechanical or electrical system. It is designed to perform a specific task and is often integrated into other devices and systems.

One key component of embedded systems is the interconnect fabric, which refers to the network of communication pathways or interconnects between various components within the system. This fabric provides the backbone for data and control transfer within the system.

The routing of data is a critical aspect of embedded systems design. On-chip interconnects utilize routing protocols to efficiently transfer data between different components on the integrated circuit. The topology of the interconnects and the choice of routing protocols greatly impact the efficiency and energy consumption of the system.

Embedded systems also require a scalable design and architecture to accommodate future expansion and integration of additional components or functionalities. This scalability allows for the system to adapt and grow as needed without requiring major redesigns or changes to the overall system architecture.

Efficient communication is crucial in embedded systems, and a well-designed network on a chip (NoC) can greatly enhance the system’s performance. NoC provides a high-bandwidth communication infrastructure that enables efficient data transfer between the various components of the embedded system.

The integration of various components and functionalities into a single chip further enhances the efficiency and compactness of embedded systems. This integration allows for reduced power consumption and improved overall performance.

The design and architecture of embedded systems must prioritize energy efficiency, as many of these systems operate on limited power sources. By optimizing the interconnects, protocols, and overall system design, energy consumption can be minimized without compromising performance.

Enhanced Communication and Integration

In the world of integrated circuits, enhanced communication and integration capabilities are essential for achieving high performance and efficiency in complex systems. This is where the concept of Network on a Chip (NoC) comes into play, revolutionizing the way chips are designed and interconnected.

NoC is a communication architecture that provides a scalable and energy-efficient solution to the ever-increasing demands of system integration. It offers a systematic way to organize and control the interconnects within a chip, allowing for efficient data transfer between different components.

One of the key advantages of NoC is its ability to overcome the limitations of traditional bus-based interconnects. With NoC, the communication fabric is organized into a network-like topology, where each component within the chip is connected through dedicated links and routing nodes. This distributed approach allows for improved scalability, as the network can easily adapt to the increasing number of components and their communication requirements.

The design of the NoC architecture plays a crucial role in ensuring efficient communication. It involves defining the routing algorithms and protocols that govern how data packets are transmitted and received within the network. With carefully designed routing algorithms, it is possible to optimize the communication paths, minimizing delays and maximizing throughput.

Integration is another key aspect of NoC, as it enables different types of components to seamlessly work together. With NoC, it is possible to integrate diverse functionalities, such as processing units, memory modules, and peripherals, on a single chip. This level of integration not only reduces the physical footprint of the system but also eliminates the need for external connections and simplifies system design.

Overall, NoC offers a powerful solution for enhancing the communication and integration capabilities of integrated circuits. By leveraging the principles of network communication, NoC enables chips to achieve higher performance, scalability, and energy efficiency, paving the way for the development of complex and advanced systems.

Real-time Processing

Real-time processing is a crucial aspect of modern integrated circuits, enabling efficient and high-performance communication and processing in various systems. The interconnect fabric plays a vital role in ensuring the effective transfer of data between different components within a chip.

The design and routing of the interconnects are critical to achieving optimal performance and energy efficiency. A well-designed communication protocol and architecture allow for seamless integration and scalability in a system, accommodating the growing demands of data processing.

The topology of the interconnects determines how efficiently the data flows between different components on the chip. A well-defined topology can minimize delays and maximize throughput, ensuring real-time processing capabilities. Additionally, the use of advanced routing algorithms can further improve the efficiency of data transfer.

The energy efficiency of real-time processing systems is of utmost importance. By optimizing the interconnect fabric and communication protocols, the energy consumption can be significantly reduced, leading to improved overall system efficiency. This is especially crucial in power-limited applications where minimizing energy consumption is essential.

In conclusion, real-time processing in integrated circuits is a complex task that requires careful consideration of various factors. Efficient interconnects, well-designed communication protocols, and energy-conscious architectures are essential for achieving high-performance and energy-efficient systems.

Internet of Things

The Internet of Things (IoT) is a network of physical objects connected to the internet, enabling them to collect and exchange data. It is a system that involves the integration of various devices, sensors, and technologies, transforming the way we interact with the physical world.

One of the key aspects of IoT is its scalable nature, allowing for the connection of a large number of devices. This scalability is crucial as IoT aims to connect billions of devices, ranging from small sensors to large smart systems. The topology of the network plays a vital role in achieving this scalability, ensuring efficient communication and data exchange.

Efficiency is a critical factor in IoT design. As devices in an IoT system are often resource-constrained, energy efficiency is of utmost importance. The system-on-a-chip (SoC) architecture is commonly used for IoT devices, as it provides integration and efficiency by combining multiple functions onto a single chip.

In an IoT network, the interconnects between devices play a crucial role in ensuring reliable and efficient communication. The routing protocol, used to guide data packets from source to destination, plays a vital role in optimizing network performance and minimizing latency.

The fabric interconnects within an IoT network need to be designed with consideration for power consumption and energy efficiency. Low-power interconnect designs, such as those utilizing asynchronous communication, can help conserve energy and extend the battery life of IoT devices.

Overall, the design and architecture of an IoT network require careful consideration of factors such as scalability, efficiency, and integration. By leveraging advanced technologies and optimizing network performance, IoT has the potential to revolutionize various industries and improve our daily lives.

Connectivity and Interoperability

Connectivity and interoperability are essential features in the design of network on a chip (NoC) architectures. NoC integrates multiple cores and supports efficient communication between them, enabling the seamless exchange of data within the system.

The design of NoC architectures focuses on optimizing various aspects, including energy consumption, performance, and scalability. By employing a hierarchical or mesh-based topology, NoCs facilitate the integration of multiple cores onto a single chip, minimizing the interconnect length and ensuring efficient communication.

Interconnects play a vital role in the efficient functioning of NoCs. Routing algorithms are used to establish optimal paths for data transmission, taking into account factors like network congestion, latency, and energy efficiency. With intelligent routing, NoCs ensure that data is delivered promptly and accurately, optimizing system performance.

NoCs also provide the flexibility to support diverse communication patterns. Through the use of network interfaces and protocols, NoCs enable the integration of different types of cores, each with varying communication requirements. This interoperability facilitates the exchange of data between cores, enhancing the overall system efficiency.

Furthermore, NoCs offer scalability, allowing for easy expansion and modification of the system. The fabric of NoCs can be extended by adding more cores, enabling the system to adapt to changing requirements. This scalability ensures the long-term viability of the integrated circuits and promotes a future-proof design.

In summary, connectivity and interoperability are crucial aspects in the design of NoC architectures. By optimizing interconnects, routing algorithms, and communication patterns, NoCs facilitate efficient data transmission, energy consumption, and system performance. The scalability of NoCs ensures their adaptability to future needs, making them a valuable solution for integrated circuits.

Data Collection and Analysis

Efficient data collection and analysis is crucial for the performance and efficiency of network-on-chip (NoC) systems. With the increasing complexity and size of integrated circuits, the interconnect fabric plays a critical role in determining the overall system performance. Proper design and integration of the interconnect fabric can optimize data communication and routing within a chip.

The choice of both the interconnect topology and the communication protocol are key factors that impact the scalability and efficiency of a network-on-chip architecture. The interconnect topology determines the physical arrangement of the interconnects, while the communication protocol governs the rules and algorithms for data transmission. Both need to be carefully considered to ensure efficient and reliable data transfer.

Data collection and analysis methods can be employed to measure and evaluate the performance and efficiency of a network-on-chip architecture. By collecting data on various parameters such as latency, throughput, and power consumption, designers can analyze the behavior of the system and identify potential bottlenecks or areas for improvement. This information can then be used to optimize the design of the interconnect fabric and routing algorithms.

Moreover, data collection and analysis can help identify any performance issues or limitations with the chosen interconnect topology or communication protocol. By analyzing the data, designers can gain insights into the system’s behavior and make informed decisions to enhance its scalability and efficiency. This iterative process of data collection, analysis, and design refinement is essential for creating high-performance network-on-chip systems.

Design and Implementation of Network on a Chip

The design and implementation of a network on a chip (NoC) play a crucial role in the performance and integration of modern integrated circuits. NoC refers to a communication infrastructure that interconnects various components within a chip using a network-like architecture. This approach allows for efficient data transfer, reduced energy consumption, and improved system scalability.

The design of an NoC involves creating an optimal interconnect topology, which determines the efficiency and performance of the system. The choice of topology depends on the specific requirements of the chip, such as the number of components, the frequency of communication, and the desired level of fault tolerance. Common topologies include mesh, torus, and tree structures.

The implementation of an NoC involves designing the routing algorithm and protocol used for data transfer. These algorithms determine how data packets navigate through the network to reach their destination, ensuring efficient and reliable communication. Additionally, the choice of routing algorithm affects the energy consumption of the chip, as well as the overall performance of the system.

In terms of integration, an NoC provides a flexible and scalable solution for interconnecting components within a chip. The network fabric can be easily adapted to accommodate changes in the system’s architecture, allowing for seamless integration of new components and functionalities. This scalability also ensures that the chip can handle increasing workloads and data traffic without compromising performance or efficiency.

Overall, the design and implementation of a network on a chip is crucial for optimizing the energy consumption, interconnect efficiency, and performance of integrated circuits. By carefully designing the interconnect topology, routing algorithms, and protocols, chip designers can create highly efficient and scalable systems that meet the demands of modern computing applications.

Architecture

The architecture of a Network on a Chip (NoC) refers to the system design and organization of the communication fabric within the integrated circuit. It aims to provide efficient and scalable interconnects for the on-chip network, which plays a crucial role in the overall performance and energy efficiency of the system.

The NoC architecture typically consists of multiple processing elements, referred to as nodes, which are interconnected through a network topology. The network fabric is responsible for routing packets and ensuring reliable communication between the nodes. It includes switches and routers that use various routing algorithms and protocol implementations to efficiently deliver data across the network.

One of the key considerations in designing the NoC architecture is scalability. The architecture should be able to handle the increasing integration of components on a chip and support the growing demand for high-performance communication. This requires a flexible and modular design that can easily accommodate changes in the number of nodes and the communication requirements of the system.

An efficient NoC architecture also takes into account the energy consumption of the network. By optimizing the routing algorithms and minimizing the distance traveled by packets, the architecture can reduce the energy overhead associated with communication. This is particularly important in energy-constrained systems, such as portable devices and Internet of Things (IoT) applications.

The choice of network topology is another critical aspect of the NoC architecture. Different topologies, such as mesh, tree, or ring, have different properties in terms of latency, bandwidth, and fault tolerance. The selection of the topology depends on the specific requirements of the application and the trade-offs between performance, area, and power.

In conclusion, the architecture of a Network on a Chip plays a crucial role in enabling efficient and scalable communication within an integrated circuit. It involves designing a network fabric that supports high-performance interconnects, optimizing routing algorithms for energy efficiency, and selecting a suitable network topology. Together, these aspects contribute to the overall performance and energy efficiency of the system.

Topology and Routing

The design of a Network on a Chip (NoC) is heavily influenced by the topology and routing choices made for the interconnect fabric. The interconnects in a NoC system provide the communication channels between different processing elements on the chip. The choice of topology determines the overall structure of the interconnect fabric, while the routing protocol determines how data is transmitted between different nodes.

The topology of a NoC architecture can be hierarchical, mesh-based, or any other design that suits the specific requirements of the system. Each topology has its own advantages and disadvantages in terms of performance, scalability, and efficiency. For example, a hierarchical topology may be more efficient for systems with a large number of nodes, while a mesh-based topology may provide better performance for systems with a smaller number of nodes.

The routing protocol used in a NoC determines how data packets are transmitted from the source node to the destination node. Different routing algorithms can be implemented, such as deterministic or adaptive routing. Deterministic routing guides packets along a predetermined path, while adaptive routing dynamically selects the path based on the current network conditions.

The choice of topology and routing protocol in a NoC design is crucial for achieving high performance and scalability. A well-designed interconnect fabric can enable efficient communication between processing elements on the chip, leading to improved system integration and overall chip performance. Additionally, by carefully considering the topology and routing options, the NoC can ensure efficient use of network resources, minimizing congestion and latency.

Communication Protocols

In a Network on a Chip (NoC) architecture, communication protocols play a crucial role in ensuring efficient and reliable data transfer between different components of the system. These protocols define the rules and mechanisms for transmitting data over the interconnect fabric of the chip.

The design of communication protocols in a NoC system involves various aspects like routing, topology, integration, and performance. Routing protocols determine how data packets are directed from the source to the destination within the network. They ensure that packets are delivered in a timely and reliable manner, optimizing factors such as energy efficiency and scalability.

Communication protocols also take into consideration the underlying interconnect fabric of the chip. This includes the physical wiring and logical connections that enable communication between different components. By efficiently utilizing the interconnects, communication protocols minimize latency and maximize throughput, resulting in better overall system performance.

Another critical aspect of communication protocols is their ability to adapt to changing network conditions. Protocol designs that can dynamically adjust their routing decisions based on real-time information help in improving the efficiency and reliability of data transfer. These adaptive protocols enhance the robustness of the network, ensuring uninterrupted communication even in the presence of faults or congestion.

The choice of communication protocols in a NoC architecture depends on the specific requirements of the system. Different protocols offer different trade-offs in terms of performance, energy efficiency, and scalability. Therefore, designers need to carefully evaluate the characteristics of each protocol and select the one that best suits their design goals and constraints.

Testing and Verification

Testing and verification are essential aspects of the design and implementation process of a Network on a Chip (NoC) system. As the scale and complexity of NoC architectures continue to increase, it becomes even more critical to ensure the correctness and reliability of the system.

Scalability is a key consideration in testing and verification. With the integration of numerous components and interconnects, it is necessary to test the system’s behavior under different loads and configurations. This involves assessing the performance of the NoC fabric, routing protocols, and communication topologies.

Energy efficiency is another important aspect to consider. As NoCs are often used in power-constrained systems, it is crucial to verify that the design minimizes energy consumption while maintaining optimal performance. This involves analyzing energy usage at various levels, including individual components and the overall system.

Protocol compliance is essential for ensuring interoperability and compatibility within the NoC system. Testing and verification must confirm that the implemented protocols adhere to the defined standards and specifications.

Furthermore, the verification process should include a thorough analysis of the routing algorithms and communication protocols employed in the NoC system. This includes testing the system’s response to different traffic patterns, evaluating the effectiveness of the routing algorithms, and analyzing the overall latency and throughput of the system.

Overall, testing and verification play a crucial role in the success of a NoC system. By thoroughly assessing the scalability, integration, energy efficiency, protocol compliance, and performance of the system, designers can ensure a reliable and efficient network architecture.

Ensuring Reliability and Performance

Network on a Chip (NoC) systems rely on efficient routing mechanisms to ensure reliability and performance. The routing architecture enables data packets to be transmitted between different components of the system seamlessly. Scalability and integration are key considerations when designing the interconnects for a NoC. By carefully planning the topology and design of the network fabric, the system can accommodate a large number of components while maintaining efficient communication between them.

Performance is a crucial aspect of any NoC, as it directly impacts the efficiency and energy consumption of the system. The interconnect design plays a crucial role in achieving optimal performance. The protocol used for communication between components can also greatly influence the overall performance of the NoC. By implementing efficient communication protocols and optimizing the network architecture, the system can achieve higher levels of performance and energy efficiency.

Reliability is another important factor to consider in NoC systems. The interconnects must be designed to ensure reliable data transmission without any loss or errors. This can be achieved through the use of error correction techniques, redundancy, and fault-tolerant mechanisms. Additionally, the network topology should be carefully planned to minimize the impact of failures on the overall system performance.

In conclusion, ensuring reliability and performance in a Network on a Chip system requires careful consideration of the routing architecture, scalability, integration, interconnect design, and communication protocols. By optimizing these factors, the system can achieve high levels of efficiency, energy savings, and reliable data transmission.

Simulation and Emulation

Simulation and emulation are essential tools for the design and evaluation of network on a chip (NoC) architectures. They allow designers to assess the performance, scalability, and energy efficiency of different network topologies and interconnect designs before implementation.

In a simulation, the behavior of the NoC is modeled using software or hardware models. This allows designers to evaluate various parameters, such as the communication delay, throughput, and energy consumption, for different traffic patterns and load scenarios.

Emulation, on the other hand, involves the use of actual hardware components to mimic the behavior of the NoC. This provides designers with a more accurate representation of the system, allowing them to identify and address potential bottlenecks and performance issues.

Simulation and emulation also play a crucial role in testing and validating the routing protocols and communication fabrics used in NoC architectures. By simulating various scenarios and traffic patterns, designers can evaluate the effectiveness and efficiency of different routing algorithms and protocols.

Moreover, simulation and emulation help in the integration of the NoC with other components on the chip. They allow designers to assess the compatibility and performance of the NoC with different processing elements, memory units, and peripherals. This enables them to optimize and fine-tune the NoC architecture for enhanced overall system performance.

In summary, simulation and emulation are indispensable tools for the design and evaluation of NoC architectures. They enable designers to assess performance, scalability, and energy efficiency, as well as validate routing protocols and interconnect designs. By utilizing these techniques, designers can optimize the design of NoCs for better integration and enhanced overall chip performance.

Future Trends and Challenges

The future of Network on a Chip (NoC) technology is expected to bring about several trends and challenges as the demand for efficient and scalable on-chip communication continues to grow. These trends will shape the design and architecture of future NoC systems, addressing the limitations and enhancing the performance of current interconnect solutions.

One of the key trends is the exploration of new NoC topologies and routing protocols that can provide improved energy efficiency and reduced latency. As the number of cores on a chip increases, optimizing the interconnects becomes crucial in order to minimize power consumption and maximize performance. New network topologies, such as hierarchical or mesh-based architectures, and innovative routing algorithms will be explored to meet these challenges.

Another trend in NoC technology is the integration of advanced communication protocols and fabrics. The development of protocols that can handle the increasing demand for data-intensive applications and provide reliable and secure communication is essential. Moreover, the integration of specialized fabrics, such as optical or wireless interconnects, may offer new opportunities for high-bandwidth and low-latency communication within NoC systems.

Scalability is a significant challenge in the future of NoC technology. As the complexity of integrated circuits continues to increase, it becomes critical to design NoC systems that can scale efficiently. This involves developing scalable routing algorithms, designing flexible and adaptive network architectures, and optimizing the overall communication system to accommodate a growing number of cores, while maintaining performance and reliability.

In conclusion, the future of NoC technology presents exciting opportunities and challenges. Efforts towards improving energy efficiency, exploring new topologies and routing protocols, integrating advanced communication protocols and fabrics, and ensuring scalability will shape the design and architecture of future NoC systems. The continuous evolution of NoC technology will enable the realization of complex and high-performance integrated circuits, pushing the boundaries of on-chip communication.

Integration with Artificial Intelligence

Network on a Chip (NoC) is a system-on-chip (SoC) integration technology that allows for the interconnection of various components on a single chip. With the advancements in artificial intelligence (AI), incorporating AI algorithms and techniques into the NoC architecture has become a promising avenue for enhancing the performance and efficiency of integrated circuits.

AI integration in NoC systems can benefit the communication infrastructure by enabling intelligent routing and resource management. By utilizing AI algorithms, the interconnects in the NoC can dynamically adapt and optimize the routing paths based on the current network conditions. This improves the overall energy efficiency and performance of the system.

Furthermore, AI can enhance the design of the NoC fabric by optimizing the topology and communication protocol. AI algorithms can analyze the system requirements and automatically generate the most efficient interconnect architecture and routing algorithms. This results in a more scalable and flexible design, capable of supporting complex on-chip communication requirements.

Moreover, AI integration in NoC systems offers opportunities for intelligent system-level optimization. By incorporating AI techniques at the chip level, it becomes possible to dynamically allocate resources and optimize communication pathways based on the application’s requirements. This can lead to significant improvements in system performance and energy efficiency.

In conclusion, the integration of artificial intelligence in Network on a Chip systems holds great potential for expanding the capabilities of integrated circuits. Through AI-powered routing, optimization, and resource allocation, it is possible to enhance the efficiency, scalability, and performance of NoC systems, ultimately leading to more advanced and intelligent integrated circuits.

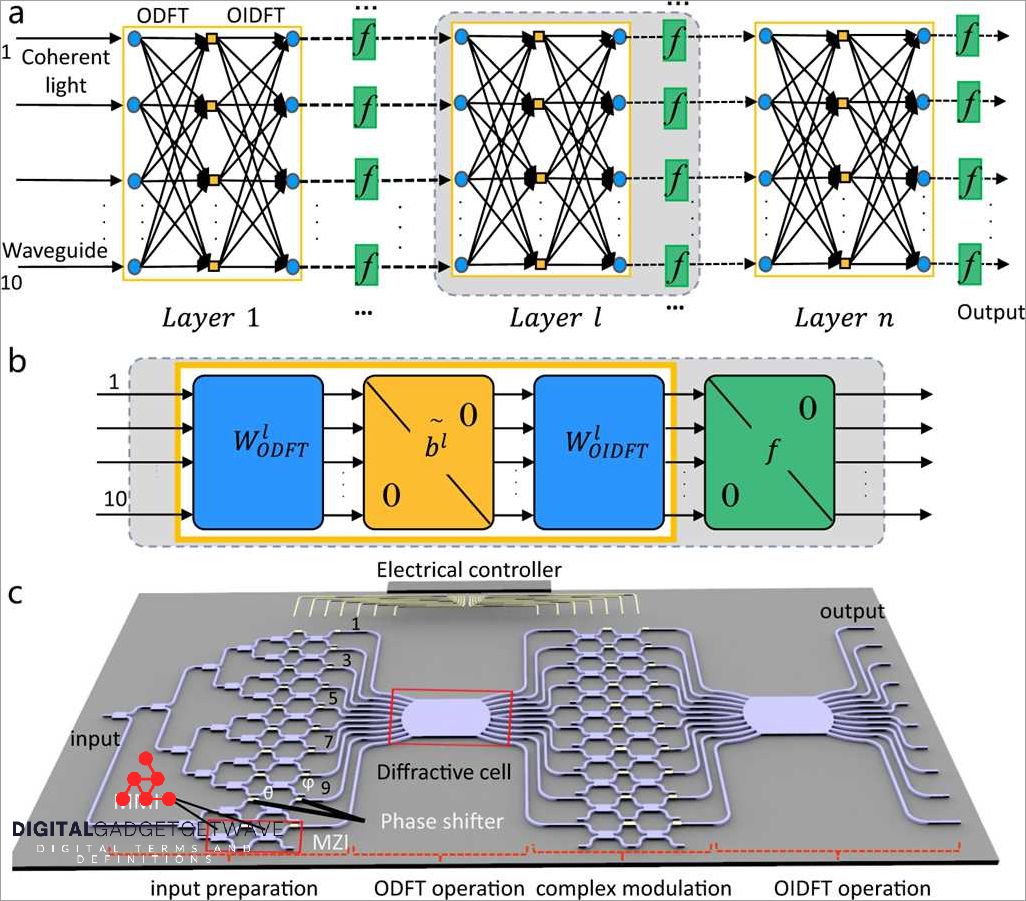

Machine Learning and Neural Networks

Machine learning and neural networks have revolutionized various fields by providing advanced capabilities for data analysis and pattern recognition. These technologies heavily rely on efficient and high-performance systems for processing large amounts of data. Network on a Chip (NoC) architecture plays a crucial role in supporting the interconnection and communication between different components of a neural network system.

The design and integration of NoCs in machine learning systems are essential for maximizing performance and energy efficiency. NoC architectures provide a fabric of interconnected communication channels that enable efficient data exchange between processing nodes. The performance of the NoC is crucial for achieving high-speed communication and reducing latency in neural networks.

The topology of the NoC is a critical factor that determines the efficiency of communication between nodes. Different topologies, such as mesh, torus, and hypercube, can be used to create efficient interconnects for neural network systems. The choice of the topology depends on the scalability and performance requirements of the system.

In addition to the physical architecture, the communication protocol used in NoCs plays a significant role in the overall efficiency of the system. Various protocols, such as wormhole and virtual cut-through, can be utilized to optimize the communication between nodes and reduce energy consumption.

Machine learning and neural network systems require high-speed interconnects to handle the massive amounts of data involved in training and inference. NoCs provide the necessary infrastructure for efficient communication between processing elements, enabling the seamless operation of the neural network system. By optimizing the design, integration, and communication protocols of NoCs, the performance and energy efficiency of machine learning systems can be significantly improved, unlocking new possibilities in artificial intelligence research and applications.

Edge Computing

Edge computing is a distributed computing paradigm that brings compute resources closer to the data source, reducing latency and improving performance. In the context of network on a chip (NoC) architectures, edge computing refers to the computation and communication capabilities located at the edges of the network.

One of the key considerations in edge computing is routing. Efficient routing algorithms and protocols are vital for enabling effective communication between nodes in the network. With the increasing complexity of NoC architectures, the routing mechanism needs to be scalable and adaptable to different system and chip configurations.

The network interconnects play a crucial role in edge computing. The topology of the network determines the efficiency of communication between nodes. Different interconnect architectures, such as mesh, torus, and hypercube, have their own advantages and disadvantages in terms of performance, energy efficiency, and scalability.

The design of the network on a chip architecture for edge computing must take into account the specific requirements of the target application. The system should be designed to handle high data rates, low latency, and reliable communication. Additionally, energy efficiency and scalability are important factors to consider in the design process.

Overall, edge computing in the context of network on a chip architectures provides a promising approach for improving the performance and efficiency of integrated circuits. By bringing compute resources closer to the edge of the network, edge computing enables faster and more efficient processing of data, leading to enhanced system capabilities and improved user experiences.

Security and Privacy

Security and privacy are crucial considerations when designing and implementing a network on a chip (NoC) system. As NoCs are used in a variety of applications, including sensitive domains such as healthcare and defense, ensuring the confidentiality, integrity, and availability of data is of utmost importance.

One of the main challenges in securing a NoC is the communication between different components within the network. The interconnects that enable efficient data transfer and routing also introduce vulnerabilities. Therefore, it is important to carefully design the network topology and architecture to minimize potential security risks.

Various security measures can be implemented at different levels of the NoC design. At the chip level, hardware-level security mechanisms such as encryption and authentication can be incorporated to protect data integrity. Additionally, protocols and algorithms can be employed to detect and prevent attacks, ensuring that only authorized components have access to the network.

Privacy is another important aspect to consider in NoC design. With the increasing amount of sensitive data being transmitted over networks, it is essential to protect the privacy of users and prevent unauthorized access. This can be achieved through the use of secure protocols, data anonymization techniques, and access control mechanisms.

To enhance the overall security and privacy of a NoC system, it is necessary to consider not only the hardware and software aspects but also the energy efficiency. By optimizing the power consumption of the network, potential attackers can be deterred, as they are less likely to target systems that are well-protected and energy-efficient.

In conclusion, security and privacy are critical considerations in NoC design. By implementing robust security measures, such as encryption, authentication, and access control, and considering energy efficiency, designers can ensure the confidentiality, integrity, and availability of data while protecting the privacy of users.

Threats and Countermeasures

Designing a network on a chip (NoC) brings several challenges and potential threats that need to be addressed. One of the main concerns is energy efficiency. As the number of components and the complexity of the network increase, the power consumption also rises. Countermeasures to address this issue include the use of power management techniques, such as clock gating and power gating, to reduce the energy consumption of idle components.

The network architecture and routing protocol also play a crucial role in determining the performance and scalability of the NoC. A poorly designed architecture or inefficient routing algorithm can result in bottlenecks and congestion, leading to decreased overall system performance. To counteract this, advanced routing algorithms and efficient interconnects can be implemented to optimize the communication fabric and improve data transfer efficiency.

Another threat to the NoC is the potential for security breaches. As the network becomes more integrated and interconnected, the risk of unauthorized access and data breaches increases. To mitigate these risks, encryption protocols and authentication mechanisms can be implemented at different layers of the NoC architecture, ensuring data confidentiality and integrity.

Lastly, the topology of the NoC is an important consideration for both performance and scalability. The choice of a topological layout can greatly impact the communication efficiency and routing complexity. For example, a mesh topology provides a regular and scalable structure, while a tree-based topology offers shorter communication paths. By carefully considering the system requirements and performance goals, the appropriate topology can be selected to optimize the overall system efficiency.

Data Protection and Encryption

Data protection and encryption are crucial aspects of a network on a chip (NoC) system, ensuring the security and privacy of data transmitted through the network. With the increasing complexity and integration of modern chip designs, efficient and reliable data protection mechanisms are essential to prevent unauthorized access and data breaches.

One of the key challenges in data protection is ensuring the efficiency of encryption and decryption processes without sacrificing system performance. Encryption algorithms that can be implemented on the chip with low computational overhead are highly desirable, as they minimize energy consumption and reduce latency. Efficient encryption algorithms enable secure communication between different nodes in the NoC, while maintaining the overall system performance.

Routing and interconnect architectures play a significant role in data protection as well. By employing a robust routing algorithm, the NoC can ensure that data packets are securely transmitted along predetermined paths, preventing interception or tampering. The scalability of the routing algorithm also allows for the integration of larger networks and expands the possibilities for chip designs.

Data protection also extends to the physical fabric of the NoC. The design of the interconnects and the network topology should be carefully considered to minimize the vulnerability to physical attacks. Redundancy and fault tolerance mechanisms can be implemented to protect against hardware-based attacks and ensure the integrity of the data transmitted within the NoC.

In conclusion, data protection and encryption are critical components of a network on a chip system. The efficiency of encryption algorithms, the routing architecture, and the physical fabric design all contribute to the overall security of the NoC. By prioritizing data protection in the design and implementation of NoC systems, chip designers can ensure the privacy and integrity of data transmitted through the network.

FAQ about topic “Network on a Chip: Expanding the Possibilities of Integrated Circuits”

What is Network on a Chip (NoC)?

Network on a Chip (NoC) is a communication architecture that integrates multiple processing cores on a single chip, allowing them to communicate with each other through a network-like structure. It is a scalable and flexible solution for enabling efficient communication between different components of an integrated circuit.

What are the advantages of using Network on a Chip (NoC) in integrated circuits?

There are several advantages of using Network on a Chip (NoC) in integrated circuits. Firstly, it provides a scalable and efficient communication infrastructure, allowing for high-bandwidth and low-latency communication between different components. Additionally, NoC can improve system performance and reduce power consumption by optimizing data routing and minimizing data transfer distance. Furthermore, NoC enables easy integration of heterogeneous components, such as different types of processors or accelerators, onto a single chip.

How does Network on a Chip (NoC) address the challenges of traditional bus-based interconnects?

Network on a Chip (NoC) addresses the challenges of traditional bus-based interconnects by providing a scalable and flexible communication architecture. Unlike a bus-based interconnect, which can become a performance bottleneck as more components are added, NoC allows for efficient communication by providing multiple communication channels and routing paths. This enables high-bandwidth and low-latency communication between components, even in complex integrated circuits.

What are the current research areas in Network on a Chip (NoC) technology?

There are several current research areas in Network on a Chip (NoC) technology. One area of research is focused on improving the energy efficiency of NoC architectures, as reducing power consumption is a key concern in modern integrated circuits. Another area of research is exploring techniques for fault-tolerant NoC designs, as reliability is critical for mission-critical applications. Additionally, researchers are investigating software and hardware co-design approaches to optimize the performance of NoC-based systems.

What are the applications of Network on a Chip (NoC) technology?

Network on a Chip (NoC) technology has a wide range of applications. One major application is in multi-core processors, where NoC enables efficient communication between different processor cores. NoC is also used in systems-on-chip (SoCs) for integrating various components onto a single chip, such as processors, memory, and peripherals. Additionally, NoC can be utilized in high-performance computing systems and in networking applications, where efficient data transfer is critical.